## MPC1100A-54-0000

High-Efficiency, Non-Isolated, Fixed Ratio, 300W, Digital DC/DC Power Module

#### NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MPC1100C-54-0002

#### DESCRIPTION

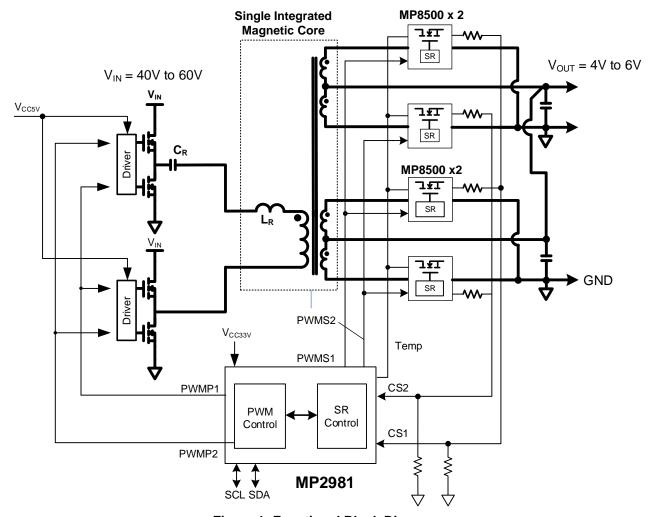

The MPC1100A-54-0000 is a high-efficiency, non-isolated LLC-DCX power card module with a fixed 10:1 transformer turns ratio. The device operates from a 40V to 60V DC primary bus and a 4V to 6V output voltage. It can deliver up to 300W of power.

The MPC1100A-54-0000 employs MPS's MP2981 (a digital LLC controller) and MP8500 (a smart synchronous rectifier). These devices can adjust the PWM to optimize the MPC1100A-54-0000, and ensure that the MPC1100A-54-0000 works at the resonant frequency.

The built-in multiple-time programmable (MTP) memory can store and restore device configurations. The fault status, input and output voltage, current, and temperature can be easily monitored via the PMBus/I<sup>2</sup>C interface.

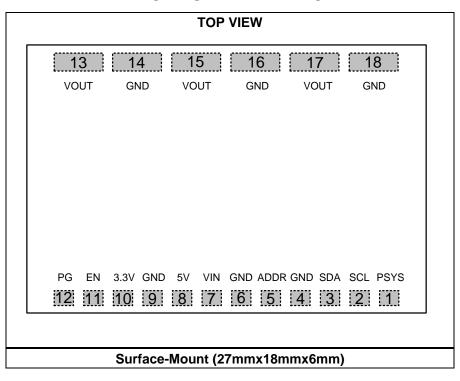

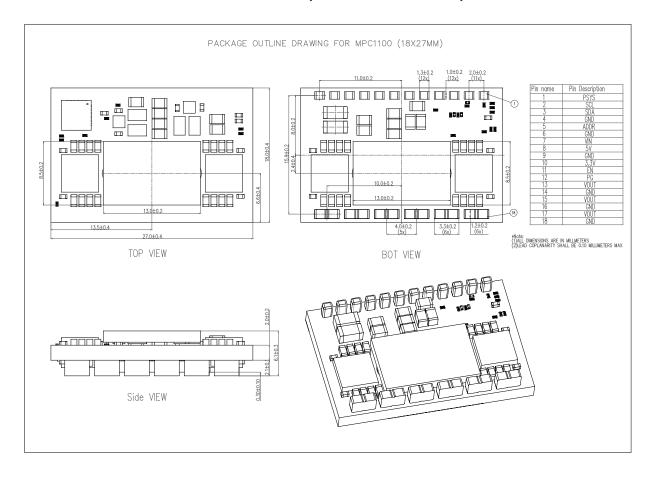

The MPC1100A-54-0000 is available in a surface-mount (27mmx18mmx6mm) package.

### **FEATURES**

- Up to 60A Continuous Secondary Current

- PMBus/I<sup>2</sup>C Compatible

- Built-In MTP to Store Custom Configurations

- Monitoring for Input Voltage, Output Voltage, Output Current, Output Power, and Temperature

- Protections Including V<sub>IN</sub> UVLO, Output OVP/UVP, OCP\_TDC, OCP\_SPIKE, and OTP

- Available in a Surface-Mount (27mmx18mmx6mm) Package

### **APPLICATIONS**

- Datacenters

- DC Power Distribution

- High-End Computing Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

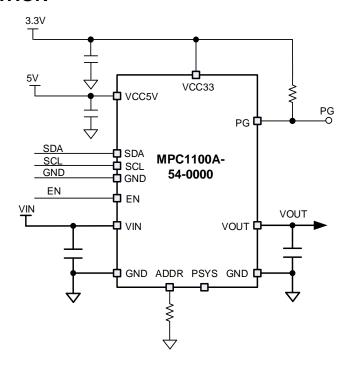

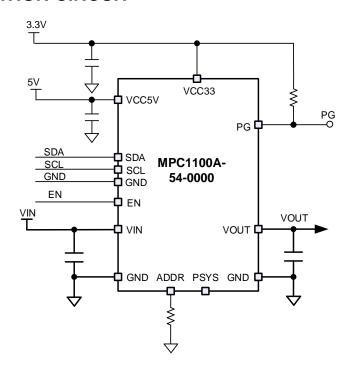

### TYPICAL APPLICATION

### ORDERING INFORMATION

| Part Number* Package |               | Top Marking | MSL Rating |

|----------------------|---------------|-------------|------------|

| MPC1100A-54-0000     | Surface-Mount | MPC1100A-54 | 3          |

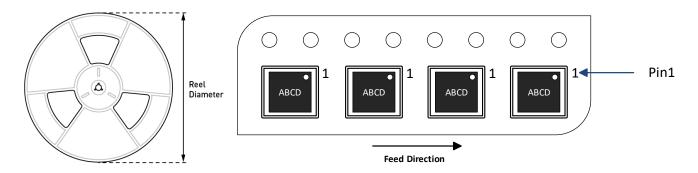

<sup>\*</sup>For Tape & Reel, add suffix –Z (e.g. MPC1100A-54-0000–Z).

### **TOP MARKING**

Date code Vendor's serial number LOT ID MPC1100A-54

### **PACKAGE REFERENCE**

© 2022 MPS. All Rights Reserved.

### **PIN FUNCTIONS**

| Pin #                  | Name | I/O    | Description                                                                                                                                                              |

|------------------------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | PSYS | A[O]   | <b>Output power indicator.</b> Current-source output. Connect a resistor from PSYS to GND to convert this current to a voltage signal.                                   |

| 2                      | SCL  | D[I/O] | PMBus/l <sup>2</sup> C clock signal.                                                                                                                                     |

| 3                      | SDA  | D[I]   | PMBus/I <sup>2</sup> C data signal.                                                                                                                                      |

| 5                      | ADDR | A[I]   | PMBus/I <sup>2</sup> C address 4-LSB pin setting.                                                                                                                        |

| 7                      | VIN  | Power  | Input main power supply.                                                                                                                                                 |

| 8                      | 5V   | Power  | <b>5V power supply input.</b> 5V is the power supply for the primary-side driver. Connect a 1µF capacitor from 5V to ground.                                             |

| 10                     | 3.3V | Power  | <b>3.3V power supply input</b> . 3.3V is the power supply for the controller (MP2981) and synchronous rectifier (MP8500). Connect a 4.7µF capacitor from 3.3V to ground. |

| 11                     | EN   | D[I]   | Enable control.                                                                                                                                                          |

| 12                     | PG   | D[O]   | Power good output. The output of PG is an open-drain signal.                                                                                                             |

| 13, 15, 17             | VOUT | Power  | Secondary-side power output.                                                                                                                                             |

| 4, 6, 9, 14,<br>16, 18 | GND  | Power  | Power ground.                                                                                                                                                            |

### **ABSOLUTE MAXIMUM RATINGS (1)**

| Supply voltage (V <sub>IN</sub> )  | 0.3V to +80V                  |

|------------------------------------|-------------------------------|

| Aux voltage (V <sub>CC33</sub> )   | 0.3V to +4.0V                 |

| Aux voltage (V <sub>CC5V</sub> )   | 0.3V to +6.5V                 |

| Address pin (ADDR)                 | 0.3V to +2.0V                 |

| Output voltage (V <sub>OUT</sub> ) | 0.3V to +7.0V                 |

| All other pins                     | $1.0.3V$ to $V_{CC33} + 0.3V$ |

| Junction temperature               | 150°C                         |

| Lead temperature                   | 260°C                         |

### Recommended Operating Conditions (2)

| Supply voltage (V <sub>IN</sub> ) | 40V to 60V                      |

|-----------------------------------|---------------------------------|

| Aux voltage (V <sub>CC33</sub> )  | 3.15V to 3.45V                  |

| Aux voltage (V <sub>CC5V</sub> )  | 4.5V to 5.5V                    |

| Operating junction temp           | (T <sub>J</sub> )40°C to +125°C |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- The device is not guaranteed to function outside of its operating conditions.

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{CC33}}$  = 3.3V,  $V_{\text{CC5V}}$  = 5V,  $V_{\text{IN}}$  = 54V,  $f_{\text{SW}}$  = 813kHz, current going into the pin is positive, typical values are at  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                            | Symbol                         | Condition                                                                                                               | Min  | Тур  | Max  | Units |

|------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Input                                                | -                              |                                                                                                                         |      |      |      |       |

| Input voltage                                        | VIN                            |                                                                                                                         | 40   | 54   | 59.5 | V     |

| Input current (V <sub>IN</sub> quiescent current)    | Ivin_q                         | Disabled, $V_{IN} = 54V$ , EN low, $V_{CC33} = 3.3V$ , $V_{CC5V} = 5V$                                                  |      |      | 200  | μΑ    |

| Input current at no load                             | Ivin_no_load                   | Enabled, $V_{IN} = 54V$ , EN high, $V_{CC33} = 3.3V$ , $V_{CC5V} = 5V$                                                  |      | 28   |      | mA    |

| Auxiliary 3.3V Supply                                |                                |                                                                                                                         |      |      |      |       |

| Supply voltage                                       | Vcc33                          |                                                                                                                         | 3.15 | 3.3  | 3.45 | V     |

| Supply current (V <sub>CC33</sub> quiescent current) | Ivcc33_Q                       | Disabled, $V_{IN} = 54V$ , EN low, $V_{CC33} = 3.3V$ , $V_{CC5V} = 5V$                                                  |      | 35   |      | mA    |

| Supply current at no load                            | I <sub>VCC33_NO_LOAD</sub>     | Enabled, V <sub>IN</sub> = 54V, EN high,<br>V <sub>CC33</sub> = 3.3V, V <sub>CC5V</sub> = 5V                            |      | 142  |      | mA    |

| Auxiliary 5V Supply                                  |                                |                                                                                                                         |      |      |      |       |

| Supply voltage                                       | V <sub>CC5V</sub>              |                                                                                                                         | 4.5  | 5    | 5.5  | V     |

| Supply current (V <sub>CC5V</sub> quiescent current) | Ivcc5v_Q                       | Disabled, $V_{IN} = 54V$ , EN low, $V_{CC33} = 3.3V$ , $V_{CC5V} = 5V$                                                  |      |      | 280  | μA    |

| Supply current at no-load                            | I <sub>VCC5V_NO_</sub><br>LOAD | Enabled, V <sub>IN</sub> = 54V, EN high,<br>V <sub>CC33</sub> = 3.3V, V <sub>CC5V</sub> = 5V                            |      | 26   |      | mA    |

| Output                                               |                                |                                                                                                                         |      | I    | I    |       |

| Transformer ratio                                    | К                              | Primary side to secondary side,<br>V <sub>IN</sub> = 54V, I <sub>OUT</sub> = 0A, K = V <sub>OUT</sub> / V <sub>IN</sub> |      | 1/10 |      |       |

| Continuous output current (3)                        | lout_dc                        | V <sub>IN</sub> = 54V, T <sub>A</sub> = 25°C                                                                            |      | 47   |      | Α     |

| Output current pulse (3)                             | I <sub>OUT_DC_PULSE</sub>      | 500μs pulse, 40V < V <sub>IN</sub> < 59.5V                                                                              | 90   |      |      | Α     |

| Output resistance (3)                                | R <sub>LL</sub>                | V <sub>IN</sub> = 54V, I <sub>OUT</sub> = 15A                                                                           |      | 3    |      | mΩ    |

| Switching frequency                                  | fsw                            | PMBus/I <sup>2</sup> C reading ton, V <sub>IN</sub> , I <sub>OUT</sub> = 1A                                             |      | 813  |      | kHz   |

| Ambient efficiency                                   | η                              | V <sub>IN</sub> = 54V, I <sub>OUT</sub> = 7.5A, T <sub>A</sub> = 25°C                                                   |      | 94   |      | %     |

| Protections                                          |                                |                                                                                                                         |      |      |      |       |

| Input voltage under-voltage lockout (UVLO)           | V <sub>IN_UVLO</sub>           | Іоит = 0А                                                                                                               | 35.5 | 37   | 39.5 | V     |

| Input voltage over-voltage protection (OVP)          | VIN_OVP                        | Latch mode, I <sub>OUT</sub> = 0A                                                                                       | 60   | 63   | 66   | V     |

| Output voltage UVP                                   | V <sub>OUT_UVP</sub>           | Latch mode, Iout = 0A                                                                                                   |      | 3.0  |      | V     |

| Output voltage OVP                                   | V <sub>OUT_OVP</sub>           | Latch mode, Iout = 0A                                                                                                   |      | 7.2  |      | V     |

| Output current over-current protection (OCP) (3)     | Іоит_ос                        | Latch mode                                                                                                              |      |      | 140  | Α     |

| Over-temperature (OT) shutdown threshold (3)         | Тотр                           |                                                                                                                         |      | 130  |      | °C    |

| OT recovery hysteresis (3)                           | T <sub>OTP_HYS</sub>           |                                                                                                                         |      | 30   |      | °C    |

| Protection recovery delay time (3)                   | tpro_delay                     |                                                                                                                         |      |      | 12.7 | ms    |

### **ELECTRICAL CHARACTERISTICS** (continued)

$V_{CC33}$  = 3.3V,  $V_{CC5V}$  = 5V,  $V_{IN}$  = 54V,  $f_{SW}$  = 813kHz, current going into the pin is positive, typical values are at  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                | Symbol              | Condition                                                | Min  | Тур   | Max  | Units |

|------------------------------------------|---------------------|----------------------------------------------------------|------|-------|------|-------|

| EN                                       |                     |                                                          |      |       |      |       |

| Low-voltage input                        | V <sub>IL(EN)</sub> |                                                          |      |       | 0.4  | V     |

| High-voltage input                       | V <sub>IH(EN)</sub> |                                                          | 0.8  |       |      | V     |

| Enable high leakage                      | I <sub>IH(EN)</sub> |                                                          |      | 3     | 8    | μΑ    |

| Enable delay (3)                         | t <sub>A</sub>      | EN high to soft start begins, Vout = 10%                 |      | 0.8   | 1    | ms    |

| PSYS                                     |                     |                                                          |      |       |      |       |

| PSYS output voltage (3)                  | V <sub>PSYS</sub>   | $V_{IN} = 54V$ , $I_{OUT} = 47A$ , $R_{SYS} = 20k\Omega$ |      | 0.634 |      | V     |

| PG Output                                |                     |                                                          |      |       |      |       |

| PG low voltage                           |                     | I <sub>PG</sub> = 20mA                                   |      | 0.1   |      | V     |

| PG high leakage current                  | $IL_{PG}$           | $V_{PG} = 3.3V$                                          | -3   |       | +3   | μA    |

| PMBus/I <sup>2</sup> C DC Characteristic | cs                  |                                                          |      |       |      |       |

| High-voltage input (3)                   | $V_{IH}$            | SCL, SDA                                                 | 1.35 |       |      | V     |

| Low-voltage input (3)                    | VIL                 | SCL, SDA                                                 |      |       | 0.8  | V     |

| Input leakage current                    |                     | SCL, SDA, ALT#                                           | -10  |       | +10  | μA    |

| Pin capacitance (3)                      | CPIN                |                                                          |      |       | 10   | pF    |

| PMBus/I <sup>2</sup> C Timing Character  | ristics (3) (4)     |                                                          |      |       |      |       |

| Operating frequency range                | f <sub>PMB</sub>    |                                                          | 10   |       | 1000 | kHz   |

| Bus free time                            | t <sub>BUF</sub>    | Between stop and start condition                         | 0.5  |       |      | μs    |

| Holding time                             | t <sub>HD_STA</sub> |                                                          | 0.26 |       |      | μs    |

| Repeated start condition set-<br>up time | t <sub>SU_STA</sub> |                                                          | 0.26 |       |      | μs    |

| Stop condition set-up time               | <b>t</b> su_sто     |                                                          | 0.26 |       |      | μs    |

| Data hold time                           | thd_dat             |                                                          | 10   |       |      | ns    |

| Data set-up time                         | t <sub>SU_DAT</sub> |                                                          | 50   |       |      | ns    |

| Clock low timeout                        | tтімеоит            |                                                          | 25   |       | 35   | ms    |

| Clock low period                         | t <sub>LOW</sub>    |                                                          | 0.5  |       |      | μs    |

| Clock high period                        | <b>t</b> HIGH       |                                                          | 0.26 |       | 50   | μs    |

| Clock/data falling time                  | t <sub>F</sub>      |                                                          |      |       | 120  | ns    |

| Clock/data rising time                   | $t_{R}$             |                                                          |      |       | 120  | ns    |

#### Notes:

<sup>3)</sup> Guaranteed by design or characterization data. Not tested in production.

<sup>4)</sup> The device supports 100kHz, 400kHz, and 1MHz bus speeds. The PMBus/I<sup>2</sup>C timing parameters in this table are for operation at 400kHz and 1MHz. If the PMBus/I<sup>2</sup>C operating frequency is 100kHz, refer to SMBus specifications for the timing parameters

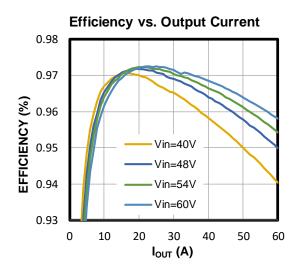

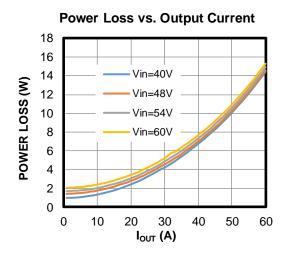

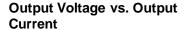

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

6

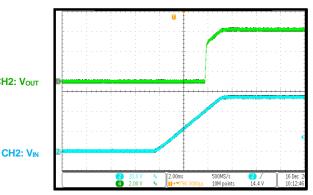

CH2: Vout

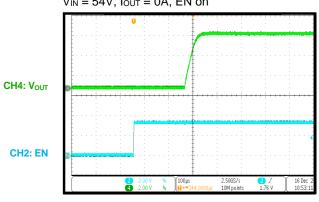

CH4: V<sub>OUT</sub>

CH2: EN

NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MPC1100C-54-0002

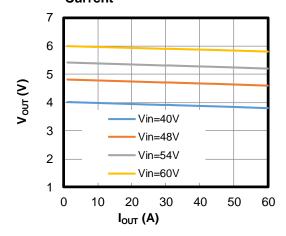

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A = 25$ °C, unless otherwise noted.

$V_{IN} = 54V$ ,  $I_{OUT} = 0A$

### Start-Up through VIN

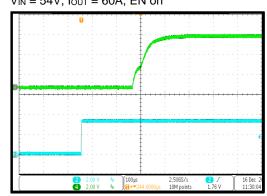

V<sub>IN</sub> = 54V, I<sub>OUT</sub> = 60A, full load

#### Remote On

$V_{IN} = 54V$ ,  $I_{OUT} = 0A$ , EN on

#### Remote On

$V_{IN} = 54V$ ,  $I_{OUT} = 60A$ , EN on

### **Transient Response**

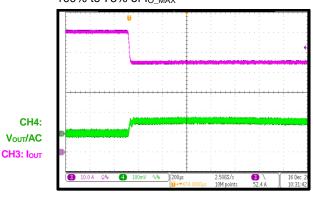

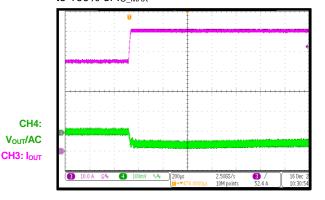

$V_{IN} = 54V$ , 1A/ $\mu$ s step change in load from 100% to 75% of  $I_{O\ MAX}$

### **Transient Response**

V<sub>IN</sub> = 54V, 1A/µs step change in load from 75% to 100% of Io MAX

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **OPERATION**

The MPC1100A-54-0000 is a full-bridge LLC-DCX power converter module with a 10:1 transformer turns ratio. The device incorporates the MP2981, a digital LLC controller that provides two PWM channels for primary-side control as well as two PWM channels for secondary-side control.

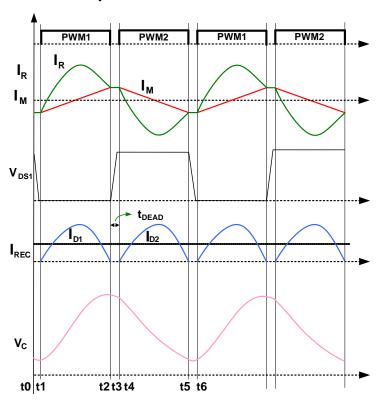

The LLC circuit is most efficient when working at the resonant frequency (see Figure 2). L<sub>R</sub> and C<sub>R</sub> have tolerances and temperature shifts that may cause the operating frequency to shift away from the resonant frequency.

The resonant frequency (fR) can be calculated with Equation (1):

$$f_{R} = \frac{1}{2\pi \times \sqrt{L_{R} \times C_{R}}}$$

(1)

With MPS's MP8500 (a smart synchronous rectifier), the MPC1100A-54-0000 can be optimized to work at the resonant frequency, which improves the module's efficiency.

MPC1100A-54-0000 incorporates four MP8500 devices. The MP8500 supports accurate current-sense (CS) functionality. Its CS pin sources a current that is proportional to the output current (5µA/A), and generates a voltage by connecting a resistor to GND. The MP2981 can use this signal to monitor and report the output current (IOUT), as well as protect the MPC1100A-54-0000 power card module.

The MP8500 can also send a zero-current detection (ZCD) signal to the MP2981 once a 0A current is detected. Then the MP2981 aligns the PWM off time and ZCD signal by fine-tuning the PWM on time (t<sub>ON</sub>) to let the MPC1100A-54-0000 operate at the resonant frequency.

During the dead time, the transformer's magnetizing inductor current discharges the FET's output capacitor to zero before the FET turns on. This helps the FET achieve zerovoltage switching (ZVS) on its primary side. The MP8500 turns off after ZCD, and then zerocurrent switching (ZCS) is implemented.

9

Figure 2: LLC Waveform

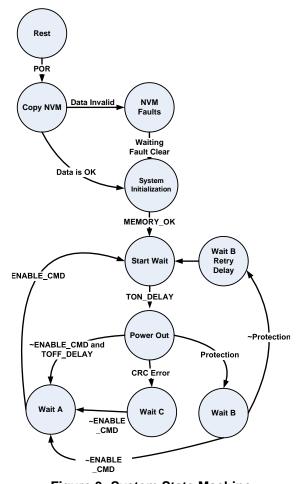

#### **Power-On Sequence**

## Multiple-Time Programmable (MTP) Memory Operation

The MP2981 uses the multiple-time programmable (MTP) memory to store the configuration parameters, including the switching frequency (f<sub>SW</sub>), soft-start time (t<sub>SS</sub>), and protection parameters. Default values are preconfigured during manufacturing. Data can be reconfigured using the STORE\_USER\_ALL command (17h) or STORE\_ALL command (15h) via the PMBus/I<sup>2</sup>C interface.

The configurations are restored by the MTP during the power-on sequence, or by receiving a RESTORE\_USER\_ALL (18h) command or RESTORE\_ALL (16h) command from the PMBus/I<sup>2</sup>C. Figure 3 shows the device's system state machine. ENABLE\_CMD means that the MSB of 01H is 1. MEMORY\_OK means that the MTP has no signature error or CRC error, or that an MTP fault state has been cleared after copying the MTP.

Figure 3: System State Machine

MTP operation can be easily accomplished with MPS's GUI software, downloaded from the MPS website. The MTP can be subjected to more than 100,000 erase and write cycles.

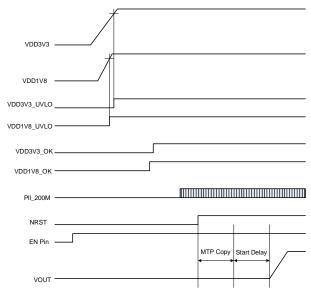

#### Start-Up Sequence

After VDD33 is ready, the internal reset of the MP2981 is released and the clock starts ticking (see Figure 4). The MP2981 begins to copy data regardless of the EN pin's state. Then the MPC1100A-54-0000 can be powered on by turning on EN, pulling VIN high, or by receiving an ON command.

Figure 4: MP2981 Start-Up Sequence

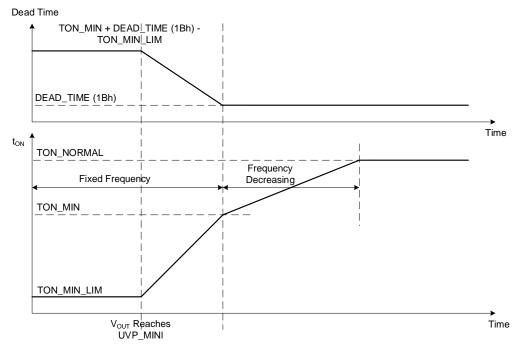

#### Soft Start

The MP2981 adopts pulse-width modulation (PWM) mode for the first PWM cycle during soft start. During the first  $t_{ON}$  increasing stage, PWM runs at the maximum frequency. The PWM on time begins at TON\_MIN\_LIM (1Fh), bits[13:8] and increases to TON\_MIN (1Ch).

The first dead time value is (TON\_MIN + DEAD\_TIME (1Bh) - TON\_MIN\_LIM). Then it drops to DEAD\_TIME (1Bh), which is the normal working value. The frequency remains the same.

During the second  $t_{\text{ON}}$  increasing stage, the PWM frequency is reduced from its maximum value to the resonant frequency.  $t_{\text{ON}}$  increases from TON\_MIN (1Ch) to TON\_NORMAL (1Eh), and the dead time is fixed. This helps reduce the inrush current during the first PWM cycles during soft start compared to traditional soft start methodology.

#### **Primary ZCD Loop**

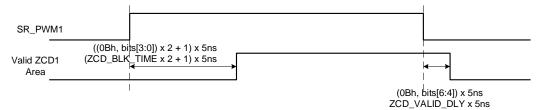

The MP2981 detects the ZCD signal from the synchronous rectifier (SR), and adjusts the PWM frequency to its resonant value according to ZCD. ZCD going high (or low, selected by SEL\_ZCD\_NEG (0Fh), bit[14]), means that the SR current goes negative. Both phases have their own ZCD, which can be enabled together or separately (0Fh, bits[6:5]).

The valid area for detecting ZCD is set by register 0Bh. For more details, see the ZCD\_TIME\_SET (0Bh) section on page 24. If the ZCD edge is within the valid setting area, toN falls by WEIGHTN\_ZCD (29h), bits[15:8]. If not, toN increases by WEIGHTP\_ZCD (29h), bits[6:0]. The adjusting speed is determined by register 29h. After 256 continuous valid ZCD pulses (including phase 1 and phase 2), toN drops by 5ns. If no valid ZCD occurs within 256 continuous PWM pulses (including phase 1 and phase 2), then toN increases by 5ns.

This function can be limited by the sampled SR current. The TDC current must be within the light-load and heavy-load limitations defined by register 0Ch if the load limit is enabled (0Ch, bits[4]).

If LOADLOW\_ZCDLOOP\_EN (0Ch), bit[15] is not enabled, the ZCD adjusting frequency can be held. The frequency can be held if any of the following conditions are met:

- The CS1 pin current is below CMP\_CS1\_ENTERFREQ (1Ah), bit[8], and 1Ah, bits[3:0] is in the corresponding valid area

- The TDC current is below or equal to the level set by MFR\_IOUT\_LEVEL\_L (49h), bits[7:0]

Under these conditions, the ZCD adjusting frequency is held since the SR's ZCD is not accurate under light-load conditions.

If the  $t_{\text{ON}}$  difference between neighboring PWM periods is within ZCDLOOP\_HYS (0Bh), bits[10:8] for 256 PWM periods, the frequency is stable unless the load changes.  $t_{\text{ON}}$  can be locked if ZCDLOOP\_LATCHTON\_EN (0Ch), bit[5] is high. The synchronized ZCD in the MP2981 is delayed from SR current ZCD timing. The final  $t_{\text{ON}}$  can be fixed by

TON\_ZCDLOOP\_DEC (0Fh), bits[11:8] if ZCDLOOP\_LATCHTON\_EN (0Ch), bit[5] is enabled.

### **Fault Monitoring and Protections**

The MPC1100A-54-0000 monitors the input voltage  $(V_{IN})$ , output voltage  $(V_{OUT})$ , output current  $(I_{OUT})$ , MP8550 temperature, and MP2981 die temperature.

The MPC1100A-54-0000 also supports various fault monitoring and protections, including  $V_{\text{IN}}$  under-voltage lockout (UVLO),  $V_{\text{IN}}$  over-voltage protection (OVP), over-current protection (OCP) spike, OCP thermal design current (TDC), output OVP, under-voltage protection (UVP), over-temperature protection (OTP), and DrMOS fault protection.

### V<sub>IN</sub> Under-Voltage Lockout (UVLO) and Over-Voltage Protection (OVP)

$V_{\text{IN}}$  is sensed and monitored by the analog-to-digital converter (ADC). The ADC-sensed input voltage is converted to an unsigned binary format (READ\_VIN (0.125V/LSB, 88h)) using the value set by VIN\_CAL\_GAIN (3Ah), which is proportional to the input voltage divider.

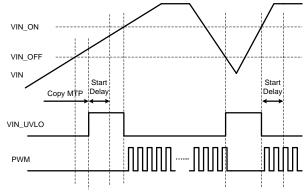

The READ\_VIN value is compared with the VIN\_ON (35h) and VIN\_OFF (36h) values to control the  $V_{\text{IN}}$  UVLO threshold. If  $V_{\text{IN}}$  is below or equal to VIN\_ON when the device is off (PWM is not generated during this time) or  $V_{\text{IN}}$  drops below VIN\_OFF at any time, then  $V_{\text{IN}}$  UVLO occurs (see Figure 5). The only exception is when the MTP is copying at start-up.

Figure 5: V<sub>IN</sub> UVLO

V<sub>IN</sub> UVLO is also enabled when both DISABLE\_ALL\_PRO (68h), bit[0] and RST\_VIN\_PRO (68h), bit[4] are low. V<sub>IN</sub> UVLO resets all shutdown protections.

If  $V_{\text{IN}}$  ramps up, EN turns on, and there is no off command, then the MPC100A-54-0000 restarts and resumes normal operation.

If  $V_{\text{IN}}$  exceeds VIN\_OV\_FLT\_LIM (40h), then  $V_{\text{IN}}$  OVP occurs and the chip shuts down. OVP does not occur when the MTP is being restored during start-up. It is controlled by registers 68h, bits[5:4] and 68h, bit[0].

# V<sub>OUT</sub> Under-Voltage Protection (UVP) and Over-Voltage Protection (OVP)

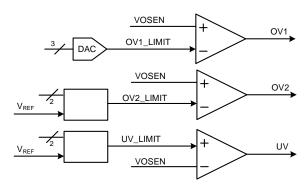

Output OVP and UVP are designed to protect the output fault statuses. If  $V_{\text{OUT}}$  exceeds the VOUT\_MAX value, the chip shuts down immediately. Based on the mode set by the VOUT\_OVP\_MAX\_LATCH bit, the part responds by going into latch-off or hiccup mode. It can also take no action if OVP is disabled.

The OVP\_MAX threshold (OVP1) has eight options ranging between 1V and 1.7V, with 0.1V/step. The over-voltage threshold (OVP2) has four tracking options: 110%, 120%, 130%, and 140% of the reference voltage (V<sub>REF</sub>).

If  $V_{\text{OUT}}$  drops quickly and falls below the UVP\_MIN threshold, the device shuts down after a short delay time (6Dh, bits[5:0]) (see Figure 6). The under-voltage threshold has four tracking options: 90%, 80%, 70%, and 60% of the reference voltage (V\_REF). Level 2 UVP (UVP2), also called  $V_{\text{OUT}}$  low protection, has four thresholds: 0.3V, 0.4V, 0.5V, and 0.6V.

Figure 6: OVP1, OVP2, and UVP Protection Circuits

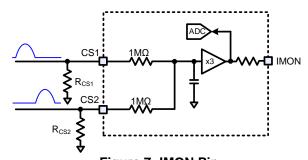

## Over-Current Protection (OCP) and Thermal Design Current (TDC)

All parallel SR DrMOS currents of the same phase flow together into their own CS resistor (R<sub>CS</sub>). Two-phase CS voltages are added after

the low-pass filter, and are then outputted on the IMON pin after a three-time buffer.

The ADC samples the IMON voltage (see Figure part 7). Then the digital calculates IOUT\_CAL\_GAIN (38h) and IOUT CAL OFFSET (39h), as READ IOUT (8Ch) from the ADC result (9Bh), which is compared to the output current limit (register 6Ah) to determine whether an overcurrent (OC) condition has occurred.

If the thermal design current (TDC) remains high for longer than the set time (6Ah), this protection shuts down the module.

Figure 7: IMON Pin

### Over-Current Protection (OCP) Spike

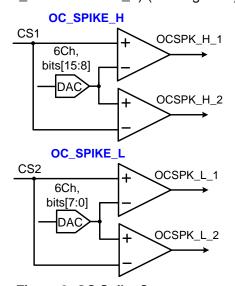

OCP is designed to limit the output current when the load consumes more current than the circuit can handle. The MP8500's CS pin sources a current that is proportional to  $I_{OUT}$  (5 $\mu$ A/A), and generates a voltage by connecting a resistor to GND. The CS pins (CS1 and CS2) of both phases are compared to the peak CS levels (OCSPK\_H and OCSPK\_L) (see Figure 8).

Figure 8: OC Spike Comparators

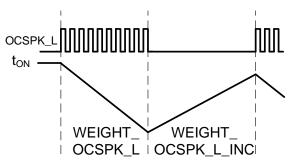

If the current drops to the lower level, the t<sub>ON</sub> accumulator decreases by the value of WEIGHT\_OCSPK\_L (32h) (see Figure 9). After dropping to a sufficient value, ton decreases by 5ns. The minimum ton value is TON\_MIN (1Ch). In each PWM cycle, the ton values for both phases are the same.

Figure 9: OCSPK L

The two OC spikes cannot shut off the chip directly.

When the OC conditions are removed, ton gradually increases to the original value of WEIGHT OCSPK H or WEIGHT OCSPK L. The greater OC value has the higher priority.

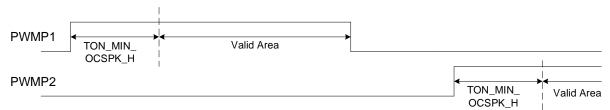

The SR\_PWM pins (PWM pins for the MP8500) are designed to turn off later than the PWMP pins (PWM signal for the primary edge) on the MP2981 during an OC spike to reduce the SR current flowing through the diodes. This is set by register 08h, bits[15:12], and bits[6:4]. See the CTRL\_OC (08h) section on page 23 for more details.

#### Over-Temperature Protection (OTP)

The SR temperature and controller temperature are both sensed by the ADC. These values trigger different responses that are independent from one another. However, the device enters latch-off or hiccup mode if either condition is triggered.

The MP8500 sends the temperature-sense signal for the MP2981's TEMP pin. If the MP8500 triggers a CS fault and enters a protection mode, it pulls the TEMP pin to 3.3V. The MP2981 must have a half-divider on the TEMP pin so that the MP2981 can send the signal to the comparator and the ADC.

#### MTP Fault

If the data in the MTP is determined to be invalid by the cyclic redundancy check (CRC), then the

system enters the MTP fault state and waits for the error to be cleared.

#### Communication Failure

A data transmission fault occurs when information is not properly transferred between the devices. There are several data transmission faults:

- Sending too little data

- Reading too little data

- Host sending too many bytes

- Reading too many bytes

- Improperly set read bit in the address byte

- Unsupported command codes

### PMBus/I<sup>2</sup>C Communication

The MPC1100A-54-0000 supports real-time monitoring for the VR operation parameters and status with PMBus/I2C.interface. Table 1 lists the monitored parameters.

Table 1: PMBus/I<sup>2</sup>C Monitored Parameters

| Parameter            | PMBus/I <sup>2</sup> C |

|----------------------|------------------------|

| Vouт                 | 62.5mV/LSB             |

| louт                 | 0.25A/LSB              |

| Temperature          | 1°C                    |

| $V_{IN}$             | 0.125V/LSB             |

| Die temperature      | 1°C                    |

| OVP                  | ✓                      |

| UVP                  | ✓                      |

| OCP                  | ✓                      |

| OTP                  | ✓                      |

| V <sub>IN</sub> UVLO | ✓                      |

| V <sub>IN</sub> OV   | ✓                      |

| CML                  | ✓                      |

### PMBus/I<sup>2</sup>C Interface

To support multiple VR devices using the same PMBus/I<sup>2</sup>C interface, the MFR ADDR PMBus register or the ADDR pin can configure the PMBus/I<sup>2</sup>C address.

The address is a 7-bit code. The 3MSB are set by the register. The 4LSB bit address can either be set by the register or by the ADDR voltage. The 00h address is reserved as an all call address, which can be set for a single chip.

The ADDR voltage is set by the voltage divider from the VDD18 voltage.

Table 2 shows the resistor values for different PMBus/I<sup>2</sup>C addresses when the 3MSB are set to 3'b010.

Table 2: Setting the PMBus/I<sup>2</sup>C Address (4LSB)

| PMBus/I <sup>2</sup> C<br>Address | Setting<br>Point (V) | R <sub>TOP</sub> (kΩ) 1% | R <sub>ВОТТОМ</sub> (kΩ) 1% |

|-----------------------------------|----------------------|--------------------------|-----------------------------|

| 20h                               | 0                    | -                        | 0                           |

| 21h                               | 0.031                | 33.2                     | 0.576                       |

| 22h                               | 0.055                | 33.2                     | 1.05                        |

| 23h                               | 0.084                | 33.2                     | 1.62                        |

| 24h                               | 0.115                | 33.2                     | 2.26                        |

| 25h                               | 0.156                | 33.2                     | 3.16                        |

| 26h                               | 0.203                | 33.2                     | 4.22                        |

| 27h                               | 0.266                | 33.2                     | 5.76                        |

| 28h                               | 0.338                | 33.2                     | 7.68                        |

| 29h                               | 0.432                | 33.2                     | 10.5                        |

| 2Ah                               | 0.542                | 33.2                     | 14.3                        |

| 2Bh                               | 0.677                | 33.2                     | 20.0                        |

| 2Ch                               | 0.845                | 33.2                     | 29.4                        |

| 2Dh                               | 1.049                | 33.2                     | 46.4                        |

| 2Eh                               | 1.301                | 33.2                     | 86.6                        |

| 2Fh                               | 1.549                | 33.2                     | 20.5                        |

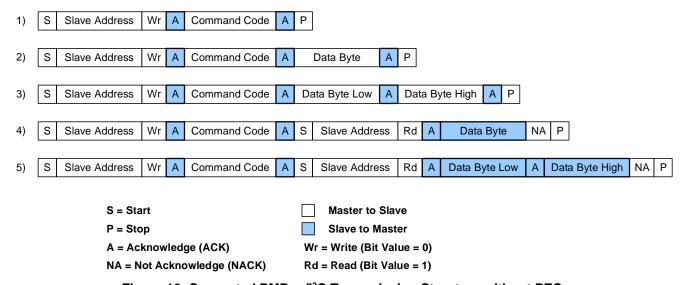

There are a total of five transmission structures, listed below:

- 1. Send command only

- 2. Write byte

- 3. Write word

- 4. Read byte

- 5. Read word

To read or write to the MPC1100A-54-0000 registers, the PMBus/I<sup>2</sup>C or I<sup>2</sup>C command must be compliant with the corresponding register and byte number.

The PMBus/I<sup>2</sup>C communication frequency can support 1MHz.

Figure 10 shows the supported PMBus/I<sup>2</sup>C transmission structure without packet error checking (PEC).

Figure 11 shows the supported PMBus/I<sup>2</sup>C transmission structure with PEC.

The PMBus/I<sup>2</sup>C or I<sup>2</sup>C commands and register map of the MPC1100A-54-0000 is the same as the MP2981. Refer to the MP2981 datasheet for additional details.

Figure 10: Supported PMBus/I<sup>2</sup>C Transmission Structure without PEC

### MPC1100A-54-0000 - NON-ISOLATED, FIXED RATIO, 300W, DIGITAL DC/DC MODULE

#### NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MPC1100C-54-0002 Wr Α Α Slave Address Command Code PEC Byte 1) S Slave Address Wr Α Command Code Α PEC Byte Α Р 2) Data Byte Α S Slave Address Wr Command Code Data Byte Low Α Data Byte High PEC Byte Α Ρ 3) Α 4) Slave Address Wr Command Code S Slave Address Rd Α Data Byte Α PEC Byte NA Ρ Slave Address Wr Command Code Α S Slave Address Data Byte Low 5) Rd Α Data Byte High Α PEC Byte NA Ρ S = Start **Master to Slave** P = Stop Slave to Master A = Acknowledge (ACK) Wr = Write (Bit Value = 0) NA = Not Acknowledge (NACK) Rd = Read (Bit Value = 1)

Figure 11: Supported PMBus/I<sup>2</sup>C Transmission Structure with PEC

### PMBUS/I<sup>2</sup>C MEMORY PAGE 0 COMMANDS/REGISTERS

| Command Code | Command Name        | Туре  | Bytes |

|--------------|---------------------|-------|-------|

| 0x00         | PAGE                | R/W   | 1     |

| 0x01         | OPERATION           | R/W   | 1     |

| 0x03         | CLEAR_FAULTS        | Send  | 0     |

| 0x04         | CTRL_PWM            | R/W   | 2     |

| 0x05         | MFR_ADC_HOLD_TIME   | R/W   | 1     |

| 0x06         | CTRL_VR             | R/W   | 2     |

| 0x07         | CTRL_MTP            | R/W   | 2     |

| 0x08         | CTRL_OC             | R/W   | 2     |

| 0x09         | LOW_POWER_SET_BIT   | R/W   | 1     |

| 0x0b         | ZCD_TIME_SET        | R/W   | 2     |

| 0x0c         | ZCD_LOOP_SET        | R/W   | 2     |

| 0x0e         | SKIP_SR_PWM_SET     | R/W   | 2     |

| 0x0f         | CTRL_PWM_BK         | R/W   | 2     |

| 0x15         | STORE_ALL           | Send  | 0     |

| 0x16         | RESTORE_ALL         | Send  | 0     |

| 0x17         | STORE_USER_ALL      | Send  | 0     |

| 0x18         | RESTORE_USER_ALL    | Send  | 0     |

| 0x19         | MFR_VOUT_SEL        | R/W   | 2     |

| 0x1A         | MFR_IOUT_SEL        | R/W   | 2     |

| 0x1B         | DEAD_TIME           | R/W   | 1     |

| 0x1C         | TON_MIN             | R/W   | 2     |

| 0x1D         | TON_MAX             | R/W   | 2     |

| 0x1E         | TON_NORMAL          | R/W   | 2     |

| 0x1F         | TON_MIN_LIM         | R/W   | 2     |

| 0x21         | MFR_REF_CONFIG      | R/W   | 2     |

| 0x22         | VOUT_TRIM           | R/W   | 1     |

| 0x25         | TRANSFORMER_RATIO   | R/W   | 2     |

| 0x29         | WEIGHT_ZCD          | R/W   | 2     |

| 0x2A         | SR_PWM_SETA_PRIDRV  | R/W   | 2     |

| 0x2B         | SS_SRNEG_SET        | R/W   | 2     |

| 0x2C         | SR_PWM_SETB         | R/W   | 2     |

| 0x2D         | MFR_SLOPE_SR        | R/W   | 2     |

| 0x2E         | MFR_SLOPE_BLK       | R/W   | 2     |

| 0x2F         | PRISETBLK_WEIGHT_SS | R/W   | 2     |

| 0x30         | WEIGHT_2_1          | R/W   | 2     |

| 0x31         | WEIGHT_4_3          | R/W   | 2     |

| 0x32         | WEIGHT_OCSPK_L_N    | R/W   | 2     |

| 0x33         | WEIGHT_OCSPK_INC    | R/W   | 2     |

| 0x34         | MFR_VIN_DROP_SET    | R/W 2 |       |

| 0x35         | VIN_ON              | R/W   | 2     |

| 0x36         | VIN_OFF             | R/W   | 2     |

| 0x38         | IOUT_CAL_GAIN       | R/W   | 2     |

| 0x39         | IOUT_CAL_OFFSET     | R/W   | 2     |

### PMBUS/I<sup>2</sup>C MEMORY PAGE 0 COMMANDS/REGISTERS (continued)

| Command Code | Command Name                      | Туре | Bytes |

|--------------|-----------------------------------|------|-------|

| 0x3A         | VIN_CAL_GAIN                      | R/W  | 2     |

| 0x3B         | VOUT_CAL_GAIN                     | R/W  | 2     |

| 0x40         | VIN_OV_FLT_LIM                    | R/W  | 2     |

| 0x42         | TEMP_GAIN_OFFSET                  | R/W  | 2     |

| 0x43         | DIETEMP_GAIN_OFFSET               | R/W  | 2     |

| 0x44         | MFR_USER_PWD                      | W    | 2     |

| 0x45         | MFR_MTP_WP                        | R/W  | 1     |

| 0x46         | SKIPDRMOS_SR_ERARLI               | R/W  | 2     |

| 0x49         | MFR_IOUT_LEVEL                    | R/W  | 2     |

| 0x4B         | MFR_VCAL_I_MAX                    | R/W  | 2     |

| 0x4C         | DC_TRIM                           | R/W  | 1     |

| 0x50         | MPS_CODE                          | R/W  | 2     |

| 0x51         | PRODUCT_CODE                      | R/W  | 2     |

| 0x52         | CONFIG_ID                         | R/W  | 2     |

| 0x53         | CONFIG_REV                        | R/W  | 2     |

| 0x5A         | CALVO_LOW_TON_SS_L                | R/W  | 2     |

| 0x5B         | TON_SS_H                          | R/W  | 2     |

| 0x5E         | POWER_GOOD_ON                     | R/W  | 2     |

| 0x5F         | POWER_GOOD_OFF                    | R/W  | 2     |

| 0x60         | PROTECT_DELAY                     | R/W  | 1     |

| 0x62         | PWRGD_DELAY                       | R/W  | 1     |

| 0x63         | START_DELAY                       | R/W  | 2     |

| 0x64         | OFF_DELAY                         | R/W  | 2     |

| 0x65         | MFR_OTP_SET                       | R/W  | 2     |

| 0x66         | MFR_DIE_OTP_SET                   | R/W  | 2     |

| 0x67         | PMBUS/I <sup>2</sup> C_ADDR_SET   | R/W  | 1     |

| 0x68         | MFR_PROTECT_CFG                   | R/W  | 2     |

| 0x69         | OVP_UVP_VID_SET                   | R/W  | 2     |

| 0x6A         | OCP_TDC_SET                       | R/W  | 2     |

| 0x6B         | OCP_SPIKE_TIMES_SET               | R/W  | 2     |

| 0x6C         | OCP_SPIKE_LEVEL                   | R/W  | 2     |

| 0x6D         | UVP_MIN_SET                       | R/W  | 1     |

| 0x79         | STATUS_WORD                       | R    | 2     |

| 0x7A         | STATUS_VOUT                       | R    | 1     |

| 0x7B         | STATUS_IOUT                       | R    | 1     |

| 0x7C         | PROTECT_SIG_GRP                   | R    | 2     |

| 0x7D         | STATUS_TEMP                       | R    | 1     |

| 0x7E         | STATUS_CML                        | R    | 1     |

| 0x80         | SYS_STATE_DBG R                   |      | 1     |

| 0x81         | FINAL_PMBUS/I <sup>2</sup> C_ADDR | R    | 1     |

| 0x82         | REG_LAST_FAULT_MTP                | R    | 2     |

### PMBUS/I<sup>2</sup>C MEMORY PAGE 0 COMMANDS/REGISTERS (continued)

| Command Code | Command Name         | Туре | Bytes |

|--------------|----------------------|------|-------|

| 0x88         | READ_VIN             | R    | 2     |

| 0x8B         | READ_VOUT            | R    | 2     |

| 0x8C         | READ_IOUT            | R    | 2     |

| 0x8D         | READ_TEMP            | R    | 1     |

| 0x8E         | READ_DIE_TEMP        | R    | 1     |

| 0x90         | USER_KEY_INPUT       | W    | 2     |

| 0x96         | READ_POUT            | R    | 2     |

| 0x99         | VIN_SENSE            | R    | 2     |

| 0x9A         | VOUT_SENSE           | R    | 2     |

| 0x9B         | IOUT_SENSE           | R    | 2     |

| 0x9C         | TEMP_SENSE           | R    | 2     |

| 0x9D         | DIE_TEMP_SENSE       | R    | 2     |

| 0x9E         | TON_PWMP             | R    | 2     |

| 0x9F         | TON_SR_PWM           | R    | 2     |

| 0xF1         | CLR_LAST_FAULT_WMTP  | Send | 0     |

| 0xF2         | READ_LAST_FAULT_TRIG | Send | 0     |

| 0xF3         | CLEAR_STORE_FAULTS   | Send | 0     |

| 0xF4         | CLEAR_MTP_FAULTS     | Send | 0     |

### **PAGE 0 REGISTER MAP**

### **PAGE (00h)**

The PAGE command configures, controls, and monitors the device through only one physical address to support normal operation, testing mode, and debugging mode.

| Command  | PAGE |                             |  |  |  |  |  |    |  |

|----------|------|-----------------------------|--|--|--|--|--|----|--|

| Format   |      | Unsigned binary             |  |  |  |  |  |    |  |

| Bit      | 7    | 7 6 5 4 3 2 1 0             |  |  |  |  |  |    |  |

| Access   | R/W  | R/W R/W R/W R/W R/W R/W R/W |  |  |  |  |  |    |  |

| Function |      | PAGE                        |  |  |  |  |  | GE |  |

| Bits | Bit Name | Description                                                                                                                                                                                                                                                                                                                                                                |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | RESERVED | Reserved. Bits[7:2] must set to 0 when changing bits[1:0].                                                                                                                                                                                                                                                                                                                 |

| 1:0  | PAGE     | 2'b00: Page 0. Normal and trim registers (read/write registers) can be stored in the MTP 2'b01: Page 1. Unused 2'b10: Page 2. Each PMBus/I <sup>2</sup> C command (not including (00h)) directly reads/writes to the MTP cells 2'b11: Page 3. Debugging/testing registers. Not stored in the MTP Users should only use Page 0 to avoid unintentionally entering test mode. |

### **OPERATION (01h)**

The OPERATION command turns the output on or off by working with the EN pin. The MPC1100A-54-0000 remains in the commanded operating mode until another different OPERATION command is sent, or the state of EN changes.

| Command  |     | OPERATION       |     |     |     |     |     |     |  |  |  |  |  |  |  |

|----------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|--|--|

| Format   |     | Unsigned binary |     |     |     |     |     |     |  |  |  |  |  |  |  |

| Bit      | 7   | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |  |  |  |  |  |

| Access   | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |  |  |

| Function |     |                 |     |     |     |     |     |     |  |  |  |  |  |  |  |

| Bits | Bit Name  | Description                                                     |

|------|-----------|-----------------------------------------------------------------|

| 7    | OPERATION | 1'b1: Turn on<br>1'b0: Turn off                                 |

| 6:0  | RESERVED  | Reserved. R/W bits are available, but do not change the device. |

#### CLEAR\_FAULTS (03h)

The CLEAR\_FAULTS command clears any fault bit in the following status registers: STATUS\_WORD (79h), STATUS VOUT (7Ah), STATUS IOUT (7Bh), STATUS TEMP (7Dh), and STATUS CML (7Eh).

This command is write-only. There is no data byte for this command.

### CTRL\_PWM (04h)

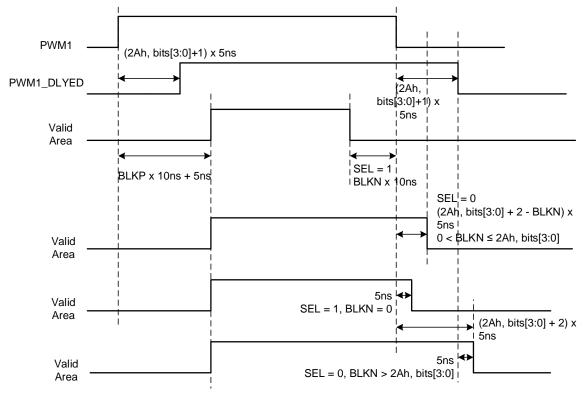

The CTRL\_PWM command controls PWM operation. The positive and negative edges of the SR\_PWM pins (SR\_PWMs) can be adjusted using the PWMP pins. The SR\_PWMs can be made to turn off earlier or later than the time set by the PWMP pins.

| Command  |     |                 |     |     |     |     |     | CTRL | _PWM |     |     |     |     |     |     |     |

|----------|-----|-----------------|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|

| Format   |     | Unsigned binary |     |     |     |     |     |      |      |     |     |     |     |     |     |     |

| Bit      | 15  | 14              | 13  | 12  | 11  | 10  | 9   | 8    | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Access   | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function |     |                 |     |     |     |     |     |      |      |     |     |     |     |     |     |     |

| Bits | Bit Name             | Description                                                                                                                                                                                                    |

|------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | RESERVED             | Reserved. R/W bits are available, but do not change the device.                                                                                                                                                |

|      |                      | Enables setting the MP2981's SKIP_EN pin high during soft start.                                                                                                                                               |

| 14   | SKIP_SS_EN           | 1'b1: Enabled. The SKIP_EN pin is pulled high during soft start 1'b0: Disabled. The SKIP_EN pin is pulled low during soft start                                                                                |

| 13   | VOUT_SKIP_EN         | Enables $V_{OUT}$ skipping. Determines what happens after $V_{OUT}$ ramps above $VOUT\_SKIP\_H$ (19h), bits[3:2], and before $V_{OUT}$ ramps below $VOUT\_SKIP\_L$ (19h), bits[1:0].                           |

| .0   | V001_01              | 1'b1: Shut down both SR_PWM pins during the dead time and after soft start. If 04h, bit[10] = 0, the primary PWMs also shut off 1'b0: No PWM shuts off                                                         |

|      |                      | Enables the primary closed loop.                                                                                                                                                                               |

| 12   | CLOSE_LOOP_EN        | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

|      |                      | Enables the primary zero-current detection (ZCD) loop.                                                                                                                                                         |

| 11   | ZCD_LOOP_EN          | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

| 10   | VOLT SKID DWMD FN    | Determines how the part responds when $V_{\text{OUT}}$ skipping is enabled and $V_{\text{OUT}}$ exceeds its limit.                                                                                             |

| 10   | VOUT_SKIP_PWMP_EN    | 1'b1: PWMP remains on when V <sub>OUT</sub> exceeds its limit during skip mode 1'b0: PWMP turns off when V <sub>OUT</sub> exceeds its limit during skip mode                                                   |

| 9    | SKIPSR_VIN_DROP_EN   | Shuts off SR_PWM if the chip detects that $V_{\text{IN}}$ is dropping quickly, or VOSEN exceeds the $V_{\text{IN}}$ ADC value.                                                                                 |

| 9    | SKIPSK_VIIN_DKOP_EIN | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

| 8:7  | RESERVED             | Reserved. R/W bits are available, but do not change the device.                                                                                                                                                |

|      |                      | Adjusts whether the SR_PWMs turn on/off before or after the PWMP pins.                                                                                                                                         |

| 6    | SR_ADJ_NORMAL_EN     | 1'b1: Enabled. If 0Fh, bit[15] and 04h, bits[4:1] are set to 1'b1, then this bit should be set to 1'b1 1'b0: Disabled. If 0Fh, bit[15] and 04h, bits[4:1] are set to 1'b0, then this bit should be set to 1'b0 |

| 5    | SR_NEG_ADJ_SS_EN     | Shuts off SR_PWM after or before PWMP during soft start, according to ton. This bit is related to registers 5Ah, 5Bh, and 2Bh.                                                                                 |

| 3    | SK_NEG_ADJ_33_EN     | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

|      |                      | Shuts off SR_PWM a fixed time before PWMP. Related to register 2Ah.                                                                                                                                            |

| 4    | SR_FIXED_DEC_EN      | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

|      |                      | Shuts off SR_PWM a fixed time after PWMP. Related to register 2Ah.                                                                                                                                             |

| 3    | SR_FIXED_EXT_EN      | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

|      |                      | Shuts off SR_PWM a fixed time before the next PWMP. Related to register 2Ch.                                                                                                                                   |

| 2    | SR_NEG_ADJ_EN        | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

|      |                      | Turns on SR_PWM after PWMP. Related to register 2Ch.                                                                                                                                                           |

| 1    | SR_POS_DEC_EN        | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                |

### MPC1100A-54-0000 - NON-ISOLATED, FIXED RATIO, 300W, DIGITAL DC/DC MODULE

### NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MPC1100C-54-0002

| 0 | CD FN | Makes SR_PWM equal to PWMP if no other adjusting function is enabled. Only enabled when the part is not in soft start, and 04h, bit[6] = 0. |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | SR_EN | 1'b1: SR_PWM = PWMP<br>1'b0: SR_PWM = 0                                                                                                     |

### MFR\_ADC\_HOLD\_TIME (05h)

The MFR\_ADC\_HOLD\_TIME command sets the waiting time between finishing one channel sampling and starting the next channel sampling.

| Command  |   |                 |                   | MFR_ADC_ | HOLD_TIME |     |     |     |  |  |  |  |  |  |

|----------|---|-----------------|-------------------|----------|-----------|-----|-----|-----|--|--|--|--|--|--|

| Format   |   | Unsigned binary |                   |          |           |     |     |     |  |  |  |  |  |  |

| Bit      | 7 | 6               | 6 5 4 3 2 1 0     |          |           |     |     |     |  |  |  |  |  |  |

| Access   | R | R/W             | R/W               | R/W      | R/W       | R/W | R/W | R/W |  |  |  |  |  |  |

| Function | Х |                 | MFR_ADC_HOLD_TIME |          |           |     |     |     |  |  |  |  |  |  |

| Bits | Bit Name          | Description                                                                         |  |  |  |  |  |  |  |  |  |  |  |

|------|-------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 7    | RESERVED          | Not defined. Read-only.                                                             |  |  |  |  |  |  |  |  |  |  |  |

| 6:0  | MFR_ADC_HOLD_TIME | The time after one channel finishes, and before the next channel starts. 100ns/LSB. |  |  |  |  |  |  |  |  |  |  |  |

### CTRL\_VR (06h)

The CTRL\_VR command configures certain chip functions, excluding pulse-width modulation (PWM).

| Command  |     | CTRL_VR |     |     |     |     |     |         |         |     |     |     |     |     |     |     |

|----------|-----|---------|-----|-----|-----|-----|-----|---------|---------|-----|-----|-----|-----|-----|-----|-----|

| Format   |     |         |     |     |     |     | L   | Insigne | d binar | у   |     |     |     |     |     |     |

| Bit      | 15  | 14      | 13  | 12  | 11  | 10  | 9   | 8       | 7       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Access   | R/W | R/W     | R/W | R/W | R/W | R/W | R/W | R/W     | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function |     |         |     |     |     |     |     |         |         |     |     |     |     |     |     |     |

| Bits | Bit Name                                  | Description                                                                                                                           |

|------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 15   | RESERVED                                  | Reserved. R/W bits are available, but do not change the device.                                                                       |

|      |                                           | Controls the analog output to enable bandgap (BG) chop.                                                                               |

| 14   | CHOP_BG                                   | 1'b1: Enabled<br>1'b0: Disabled                                                                                                       |

|      |                                           | Selects the PSYS current rate by sending different READ_POUT (96h) data.                                                              |

| 13   | PSYS_SEL_2W                               | 1'b1: 2 with LSB, send READ_POUT (96h), bits[10:1] to the 10-bit PSYS digital-to-analog converter (DAC)                               |

|      |                                           | 1'b0: 1 with LSB, send READ_POUT (96h), bits[9:0] to the DAC                                                                          |

|      |                                           | Enables the DC loop.                                                                                                                  |

| 12   | DC_CAL_EN                                 | 1'b1: Enabled<br>1'b0: Disabled                                                                                                       |

|      |                                           | Selects the die temperature's voltage vs. temperature (V-T) rate.                                                                     |

| 11   | DIE_TEMP_RATE_NEG                         | 1'b1: Negative<br>1'b0: Positive                                                                                                      |

| 10:9 | RESERVED                                  | Reserved. R/W bits are available, but do not change the device.                                                                       |

| 8    | PMBUS/I <sup>2</sup> C_ADDR_<br>KEEP_SAMP | 1'b1: The ADC constantly samples the ADDRP pin<br>1'b0: The ADC samples ADDRP only seven times after the MTP address reaches<br>8'h20 |

| 7:4  | PMBUS/I <sup>2</sup> C_FILTER_SET         | PMBus/l <sup>2</sup> C filter on the digital side. 10ns/LSB.                                                                          |

| 3 | WAIT_VIN_START            | 1'b1: Wait until $V_{\text{IN}}$ is ready (READ_VIN > VIN_ON) before ramping $V_{\text{REF}}$ and generating PWMs 1'b0: Do not wait until $V_{\text{IN}}$ is ready (READ_VIN > VIN_ON) before ramping $V_{\text{REF}}$ and generating PWMs                                                                                                                                       |

|---|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | SEL_PWRGD_1REF_<br>0TON   | Selects V <sub>REF</sub> ramping or to <sub>N</sub> increasing to act as the PG reference.  1'b1: V <sub>REF</sub> 1'b0: t <sub>ON</sub>                                                                                                                                                                                                                                         |

| 1 | MFR_ONOFFDLY_CLK_<br>1L0S | Selects the counting clock for START_DELAY and OFF_DELAY during start-up and shutdown.  1'b1: 20kHz 1'b0: 50kHz                                                                                                                                                                                                                                                                  |

| 0 | KEEP_TON_MIN_LMT_SS       | Determines the V <sub>OUT</sub> threshold before increasing to <sub>N</sub> during soft start.  1'b1: t <sub>ON</sub> stays at the TON_MIN_LIM (1Fh) value and does not increase until V <sub>OUT</sub> exceeds VOUT UVP_MIN (19h)  1'b0: t <sub>ON</sub> does not stay at the TON_MIN_LIM (1Fh) value, and begins increasing before V <sub>OUT</sub> exceeds VOUT UVP_MIN (19h) |

### CTRL\_MTP (07h)

The CTRL\_MTP command sets the MTP parameters. It is recommended to use the vendor's preset configurations.

| Command  |     |                 |     |     |     |     |     | CTRL | _MTP |     |     |     |     |     |     |     |

|----------|-----|-----------------|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|

| Format   |     | Unsigned binary |     |     |     |     |     |      |      |     |     |     |     |     |     |     |

| Bit      | 15  | 14              | 13  | 12  | 11  | 10  | 9   | 8    | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Access   | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function | Χ   |                 |     |     |     |     |     |      |      |     |     |     |     |     |     |     |

| Bits | Bit Name                | Description                                                                                                                                                                                               |

|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                         | Enables cyclic redundancy check (CRC) for the MTP user.                                                                                                                                                   |

| 15   | CRC_FAULT_USER_EN       | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                           |

|      |                         | Enables CRC for the MTP trim.                                                                                                                                                                             |

| 14   | CRC_FAULT_TRIM_EN       | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                           |

| 13   | CRC_FAULT_TOT_EN        | Enables CRC for the total MTP. Do not set this bit to 1 when using 17h (STORE_USER_ALL) to write to the MTP.                                                                                              |

| 13   |                         | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                           |

|      | MTD FAULT BLOCK         | Determines whether an MTP fault prevents start-up, including the signature fault and CRC fault.                                                                                                           |

| 12   | MTP_FAULT_BLOCK_<br>EN  | 1'b1: Enabled. If an MTP fault occurs, the chip enters the MTP fault state, and a CLEAR_MTP_FAULTS (F4h) command must be sent to exit the state 1'b0: Disabled. The chip starts up if an MTP fault occurs |

|      |                         | Prevents start-up if the data read from the MTP LAST_FAULT_ADDR is not 0.                                                                                                                                 |

| 11   | LAST_FAULT_BLOCK_<br>EN | 1'b1: Enabled. If the last fault exists, the chip must receive a CLEAR_STORE_FAULTS (F3h) command to start up 1'b0: Disabled. The chip starts up, even if the last fault exists                           |

| 10:6 | RESERVED                | Reserved. R/W bits are available, but do not change the device.                                                                                                                                           |

| 5 | CAL_FAULT_CRC_DIS           | 1'b1: Do not include MTP_FAULT_RECORD_ADDR (the 2 bytes in the MTP that store protection faults, such as OVP) when calculating CRC_TOT 1'b0: Include MTP_FAULT_RECORD_ADDR when calculating CRC_TOT |

|---|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | NO_FAULT_STORE              | 1'b1: Store 00h data to MTP_FAULT_RECORD_ADDR 1'b0: Store the value of MEMORY_ADDR (7Ah) to MTP_FAULT_RECORD_ADDR when storing is not triggered by a fault                                          |

| 3 | FAULT_SINGLE_EN             | 1'b1: Only store the 2-byte MTP_FAULT_RECORD_ADDR 1'b0: Store the whole third section of the MTP when storing FAULT_RECORD                                                                          |

| 2 | RESERVED                    | Reserved. R/W bits are available, but do not change the device.                                                                                                                                     |

| 1 | PROTECT_FAULT_<br>RECORD_EN | Enables FAULT_RECORD.  1'b1: Enabled 1'b0: Disabled                                                                                                                                                 |

| 0 | MFR_MTP_COPY_EN             | Reads the MTP (16h or 18h or F6h) when the device outputs power; ineffective for the READ_LAST_FAULT command (F2h) or the reading MTP commands (16h or 18h or F6h) on Page 2.                       |

|   |                             | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                     |

### CTRL\_OC (08h)

The CTRL\_OC command configures the over-current (OC) spike function. The PWM t<sub>ON</sub> is reduced when an OC spike occurs, and recovers after the OC spike condition is removed (see Figure 12). This protection cannot directly shut down the chip.

Figure 12: OCSPK\_H

| Command  |     | CTRL_OC         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|----------|-----|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Format   |     | Unsigned binary |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Bit      | 15  | 14              | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Access   | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function |     |                 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Bits  | Bit Name                 | Description                                                                                                                                                                                                                                   |

|-------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | SR_DLY_OCSPK             | Sets the time lengths of the SR_PWM pins' wait period before turning off after the PWMP pins when an over-current (OC) spike occurs. If any bit between bits[6:4] of this command is high, there must be a <1Bh (dead time setting). 5ns/LSB. |

| 11:8  | TON_MIN_OCSPK_H          | If an OC spike occurs on CS1 (OCSPK_H), the minimum ton can be calculated with the equation below:                                                                                                                                            |

|       |                          | (TON_MIN_OCSPK_H + 1) x 5ns                                                                                                                                                                                                                   |

| 7     | RESERVED                 | Reserved. R/W bits are available, but do not change the device.                                                                                                                                                                               |

| 6     | SR_DLY_OCSPK_H_<br>SS_EN | Turns off the SR_PWM pins after the PWMP pins if an OC spike occurs on CS1 (OCSPK_H) during soft start.                                                                                                                                       |

| б     |                          | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                                                                                                               |

|   | •                  |                                                                                                                                                    |

|---|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | SR_DLY_OCSPK_H_EN  | Turns off the SR_PWM pins after the PWMP pins if an OC spike occurs on CS1 (OCSPK_H) during a time that is not soft start.                         |

| 5 | SK_DLT_OCSFK_H_EN  | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                    |

| 4 | SB DLV OCSDIC I EN | Turns off the SR_PWM pins after the PWMP pins if an OC spike occurs on CS1 (OCSPK_H) during normal operation.                                      |

| 4 | SR_DLY_OCSPK_L_EN  | 1'b1: Enabled. Bit[5] must be set to 1'b1 1'b0: Disabled                                                                                           |

| 2 | 3 OC_TRIG_SR_EN    | Turns on the SR_PWM pins immediately if they are not on when an OC spike occurs on CS1 or CS2 (OCSPK_H or OCSPK_L, respectively) while PWMP is on. |

| 3 |                    | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                    |

|   | OCSPK_H_TON_SS_    | Adjusts ton if an OC spike occurs on CS1 (OCSPK_H) during soft start.                                                                              |

| 2 | EN                 | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                    |

| 4 | OCCUL II TON EN    | Adjusts $t_{\text{ON}}$ if an OC spike occurs on CS1 (OCSPK_H) during a time that is not soft start.                                               |

| 1 | OCSPK_H_TON_EN     | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                    |

| 0 | OCCUL TON EN       | Adjusts $t_{\text{ON}}$ if an OC spike occurs on CS2 (OCSPK_L). This cannot be adjusted during soft start.                                         |

| 0 | OCSPK_L_TON_EN     | 1'b1: Enabled<br>1'b0: Disabled                                                                                                                    |

### LOW\_POWER\_SET\_BIT (09h)

The LOW\_POWER\_SET\_BIT command controls low-power mode.

| Command  |   | LOW_POWER_SET_BIT |   |   |   |   |     |     |  |  |

|----------|---|-------------------|---|---|---|---|-----|-----|--|--|

| Format   |   | Unsigned binary   |   |   |   |   |     |     |  |  |

| Bit      | 7 | 6                 | 5 | 4 | 3 | 2 | 1   | 0   |  |  |

| Access   | R | R                 | R | R | R | R | R/W | R/W |  |  |

| Function | Х | Х                 | Х | Х | Х | X |     |     |  |  |

| Bits | Bit Name          | Description                                                                                                             |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------|

| 7:2  | RESERVED          | Not defined. Read-only.                                                                                                 |

| 1    | RESERVED          | Reserved. R/W bits are available, but do not change the device.                                                         |

| 0    | LOW_POWER_SET_BIT | 1'b1: The chip remains in low-power mode when the EN pin is low 1'b0: The chip operates normally when the EN pin is low |

#### ZCD\_TIME\_SET (0Bh)

The ZCD\_TIME\_SET command configures frequency adjusting via the zero-current detection (ZCD) function (primary ZCD loop). Figure 13 on page 25 shows the valid ZCD1 area for this function. The valid ZCD2 area is determined by SR\_PWM2. When ZCD occurs within the valid area, ton decreases by WEIGHTN\_ZCD (29h), bits[15:8]. When a ZCD event occurs outside the valid area, ton increases by WEIGHTP\_ZCD (29h), bits[6:0].

Frequency adjusting completes if the following conditions are met:

- The difference between neighboring ton values is within ZCDLOOP\_HYS (0Bh), bits[10:8] for more than 256 periods.